数字逻辑-two

你👱🏻觉得从第二章开始就好像是黄金局到铂金局

你👱🏻觉得边复习边写Blog可以起到监督你👱🏻的作用。你👱🏻今天多少沾点偷懒就被拷问了 于是你👱🏻关闭Apex Legends开始复习

你👱🏻听说下周就要考数字逻辑了,但是你👱🏻一点都不会,所以你👱🏻必须做点权衡了,先抢救下数字逻辑。

(里面的很多图片都是你👱🏻搞的别处的,必须声明一下防止被🐏,你👱🏻只是个搬运工 但是你👱🏻还是发表点看法)

组合逻辑电路

组合逻辑电路分析

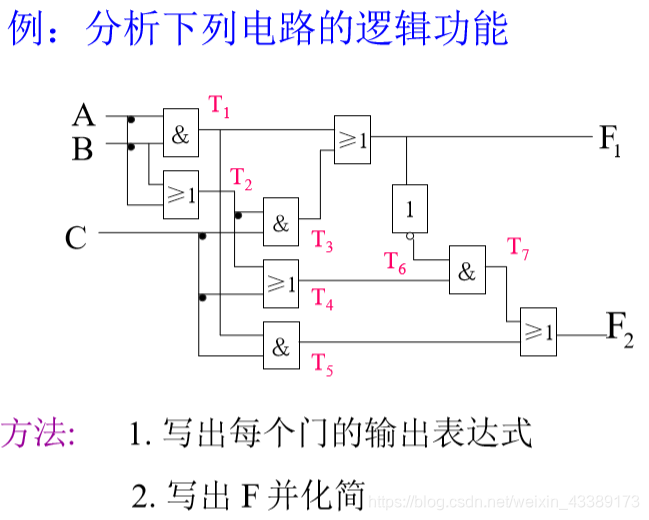

一般步骤:

1.根据输入逐级写出输出内容

2.化简逻辑功能

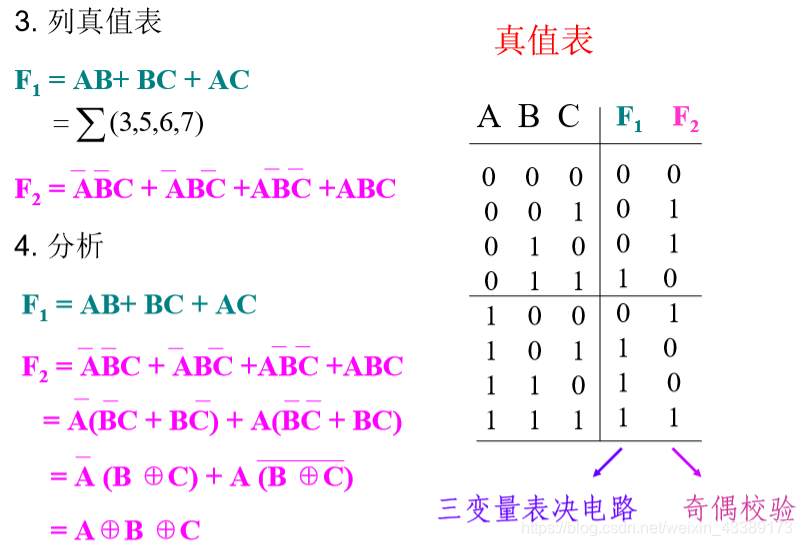

3.列出真值表

4.讨论功能

你👱🏻:听你👱🏻的话就按这么来

例题:

组合逻辑电路设计

步骤:

1.确定输入、输出以及它们之间的关系

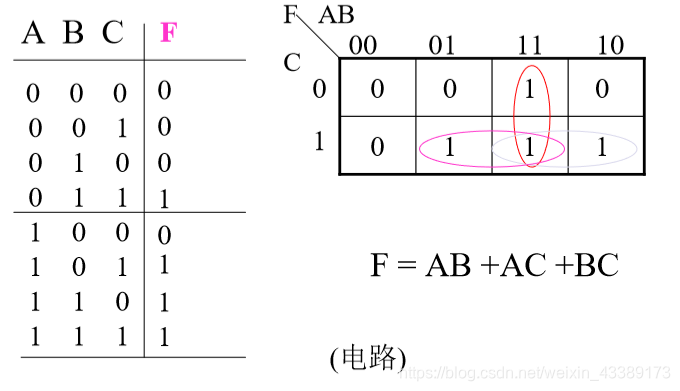

2.列出真值表

3.化简

4.画出逻辑电路图

你👱🏻:同⬆️

例题:

组合逻辑电路中的竞争冒险

目前你👱🏻看到了对于竞争的两个版本:

一个是🚪电路两个输入信号同时向相反的逻辑电平跳变(一个从0变为1,一个从1变为0)的现象就叫做竞争。

一个是在组合逻辑电路中,某个输入变量通过两条或两条以上的途径传到输出端,由于每条途径延迟时间不同,到达输出🚪的时间就有先有后,这种现象称为竞争

但其实这两个概念都对,因为第一个概念针对的是竞争冒险的适用(经常出现的)情况,第二个是竞争冒险产生的根本原因。

所以你👱🏻必须澄清下了

竞争冒险是啥呢,你👱🏻:由于竞争而在电路输出端可能产生错误(脉冲尖峰)的现象

需要你👱🏻和你注意的是,不管是哪种竞争的概念,竞争都不会必然引起竞争—冒险现象。

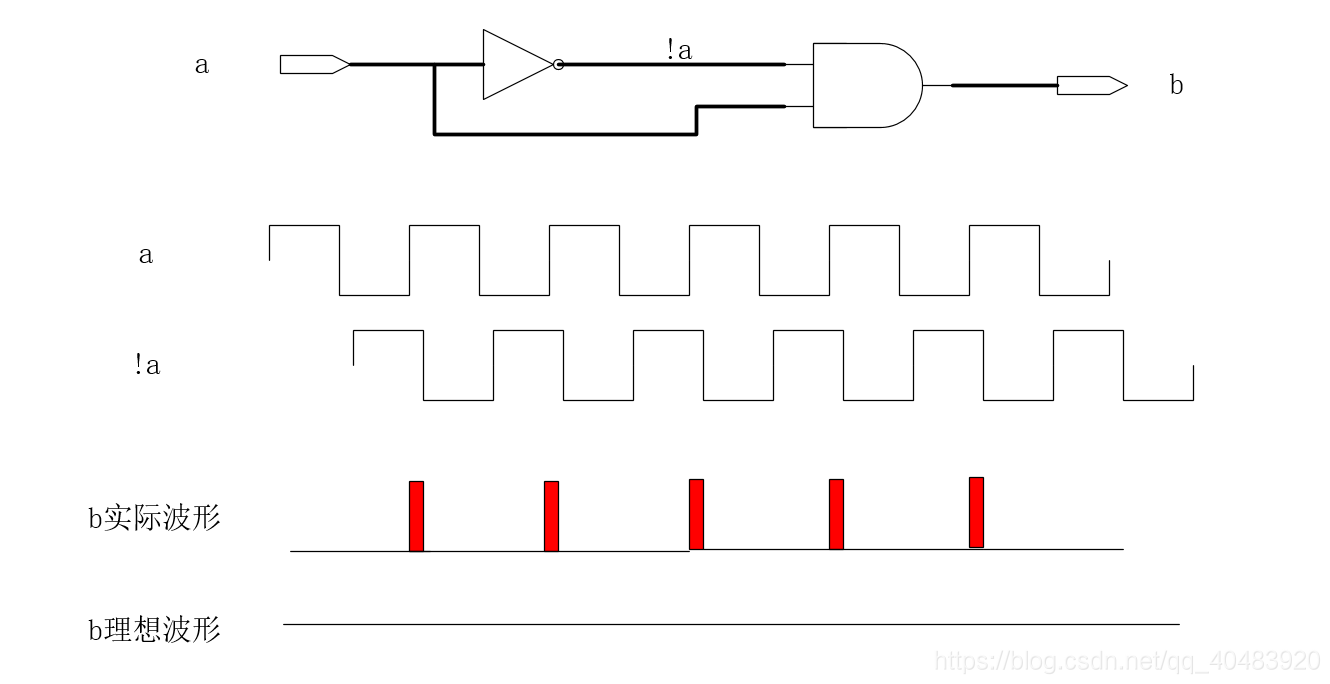

下面你👱🏻画个时序图来说明竞争冒险的成因

如上图,可以看到!a并不是与a完全对称,而是有一定延迟,这是因为在电路中,传输有一定的延迟,一个非门也有延迟。在a从0变为1之后一段时间,这时候!a还为高,并没有在a从0变为1的同时从1变为0。最终出现了尖峰脉冲。

消除方法

1、接入滤波电容

因为尖峰脉冲一般都很窄(多在几十ns以内),所以只需要在输出端接一个很小的滤波电容,就可以将尖峰脉冲的宽度削弱至电路的阈值电压以下。但输出波形随电容变化,所以适用于对波形前、后沿无严格要求的场合。

你👱🏻:什么掩耳盗铃

2、引入选通脉冲。

选通脉冲在输出稳定之后才拉高,所以可以消除稳定之前的尖峰脉冲。但是,使用这种方法,必须得到一个与输入信号同步的选通脉冲,对它的宽度和作用时间有严格的要求。

你👱🏻:什么精准礼仪

3、修改逻辑设计,增加冗余项。

但使用范围有限,考虑的情况比较多,在不同输入的时候,冗余项会不一样,所以如果考虑所有情况,会花费比较多的资源,如果设计的好,适用范围可以适当增加。

你👱🏻:什么暗度陈仓

你👱🏻觉得这个应该就做个了解吧,填空选择考考就扎不多得嘞。

常用的中规模组合逻辑标准构件

选择器

你👱🏻:觉得从这里开始多少沾点难度了

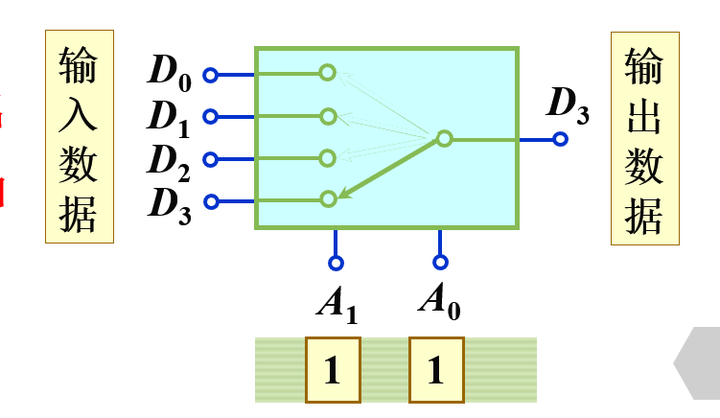

数据选择器:从多路数据输入中选择其中一路送到输出端

A1 A0为地址信号,A1A0就构成了选择

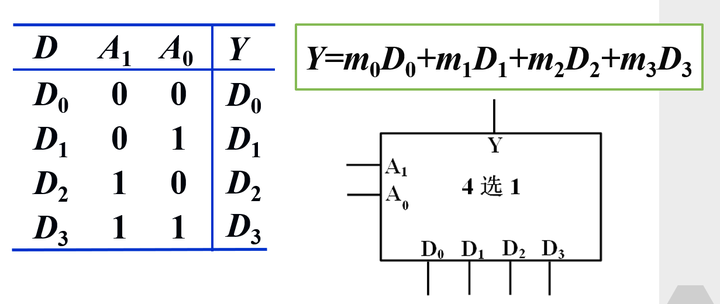

4选1数据选择器真值表

四选一多路选择器:集成芯片74153,使能端:低电平有效

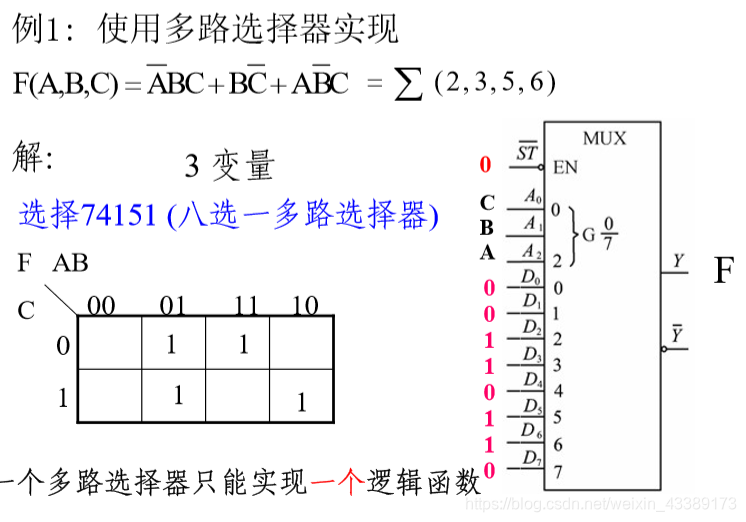

八选一多路选择器:集成芯片74151,使能端:低电平有效

例题: